## The Pseudo-NMOS Load

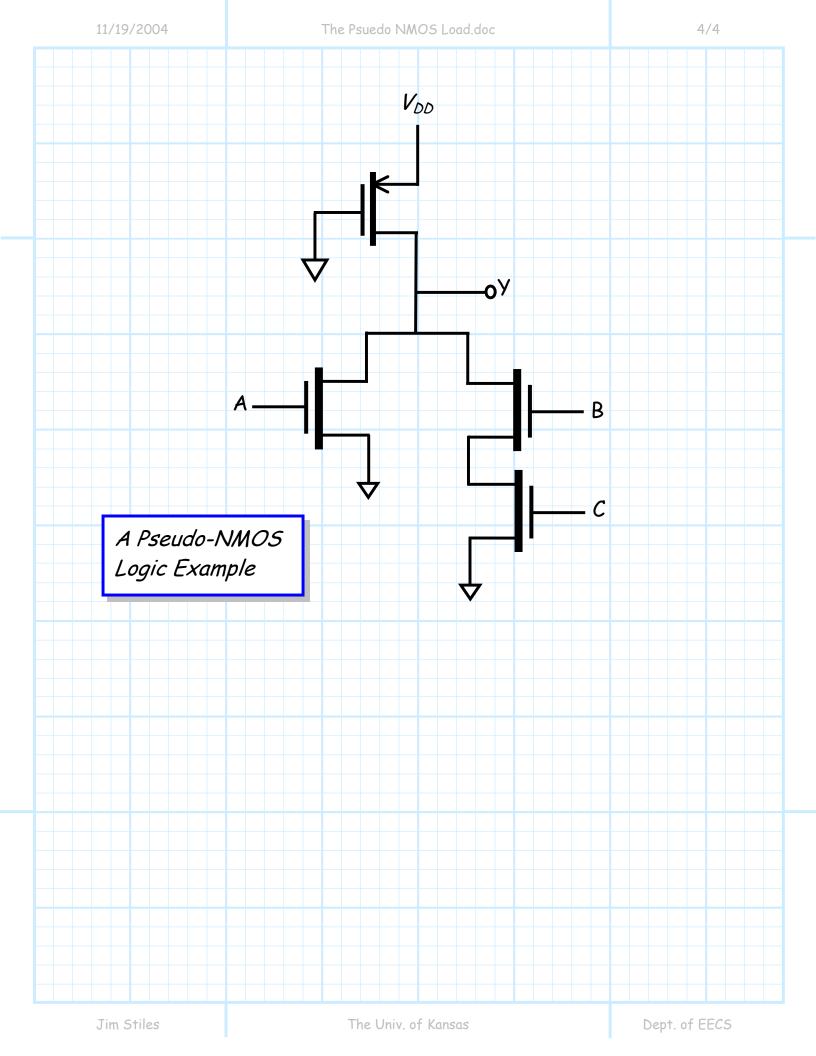

There is another type of active load that is used for NMOS logic, but this load is made from a PMOS transistor!

Hence, NMOS logic that uses this load is referred to as **Pseudo NMOS Logic**, since not all of the devices in the circuit will be NMOS (the **load** will be **PMOS**!).

We therefore call this load the "Pseudo NMOS Load", since it is the load used in Pseudo NMOS logic. But, keep in mind that the pseudo NMOS load is made from a PMOS device (this can cause great confusion!).

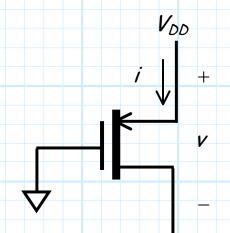

$$i_{D} = i$$

$$v_{GS} = 0 - V_{DD} = -V_{DD}$$

$$v_{DS} = -v$$

$$v_{GS} - V_{t} = -(V_{DD} + V_{t})$$

The Pseudo-NMOS Load

Note that  $v_{GS} = -V_{DD} < V_{\tau}$ , so that the load is **not** in cutoff—it can either be in **saturation or triode**.

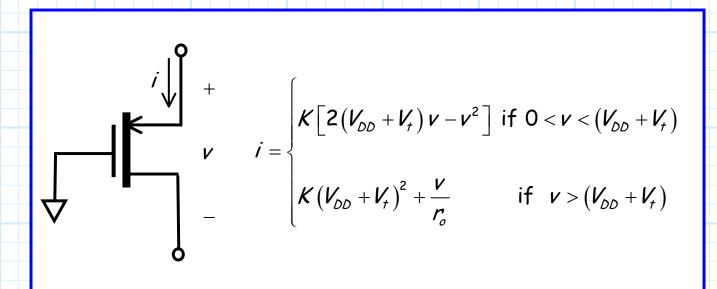

The PMOS will be in triode if:

$$V_{DS} > V_{GS} - V_t$$

$-V > -(V_{DD} + V_t)$

$V < (V_{DD} + V_t)$

In which case the current is:

$$i_{D} = K \left[ 2 \left( V_{GS} - V_{t} \right) V_{DS} - V_{DS}^{2} \right]$$

$$i = K \left[ -2 \left( V_{DD} + V_{t} \right) \left( -V \right) - \left( -V \right)^{2} \right]$$

$$i = K \left[ 2 \left( V_{DD} + V_{t} \right) V - V^{2} \right]$$

Likewise, the PMOS will be in saturation if:

$$V_{DS} < V_{GS} - V_t$$

$-V < -(V_{DD} + V_t)$

$V > (V_{DD} + V_t)$

In which case the current is:

$$i_{D} = K \left( V_{GS} - V_{t} \right)^{2} - \frac{V_{DS}}{r_{o}}$$

$$i = K \left( V_{DD} + V_{t} \right)^{2} + \frac{V}{r_{o}}$$

Jim Stiles The Univ. of Kansas Dept. of EECS

where in this case:

$$r_o = \frac{1}{\lambda K (v_{GS} - V_t)^2} = \frac{1}{\lambda K (V_{DD} + V_t)^2}$$

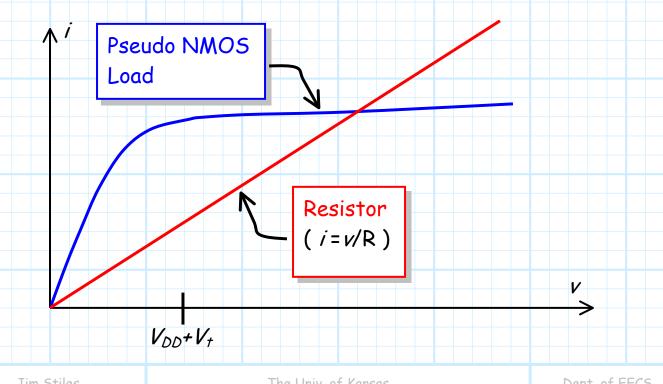

Combining these two results, we find that the pseudo NMOS load behaves very much like the depletion load:

Jim Stiles The Univ. of Kansas Dept. of EECS